News

3D TSV Packages Market Segments and Forecast By End-use Industry 2016-2026

Currently, 3D Packaging using Through Silicon Via technology (3D TSV) is one of the hottest topics in the semiconductor ecosystem. 3D TSV is vertical electrical connection (via) passing completely through a silicon wafer or die. These short vertical interconnects are replacing the long interconnects of 2D packaging technologies including wire-bond and flip chips.

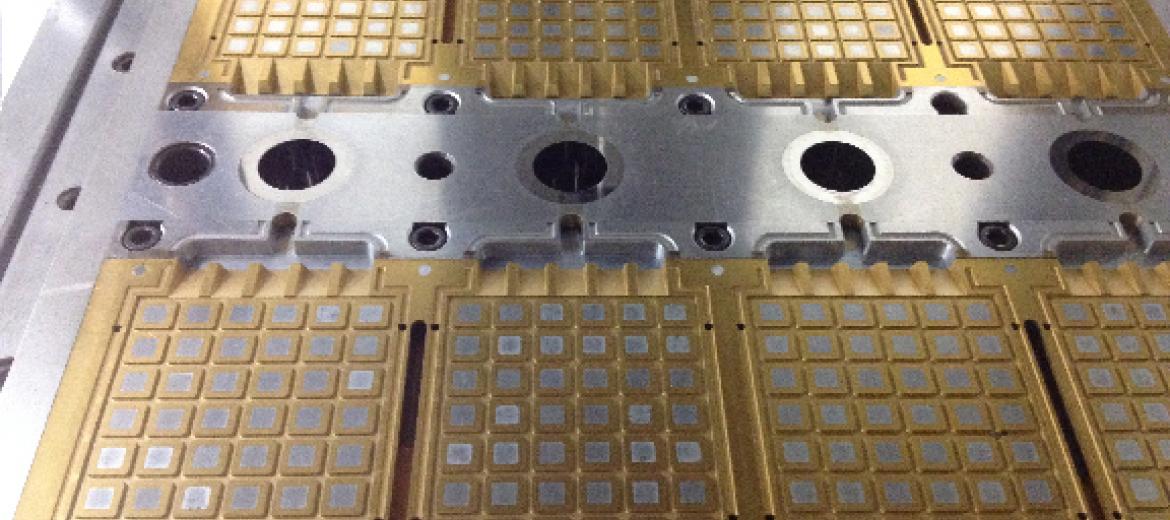

Packaging Automation Overcomes Optoelectronic Component Variety

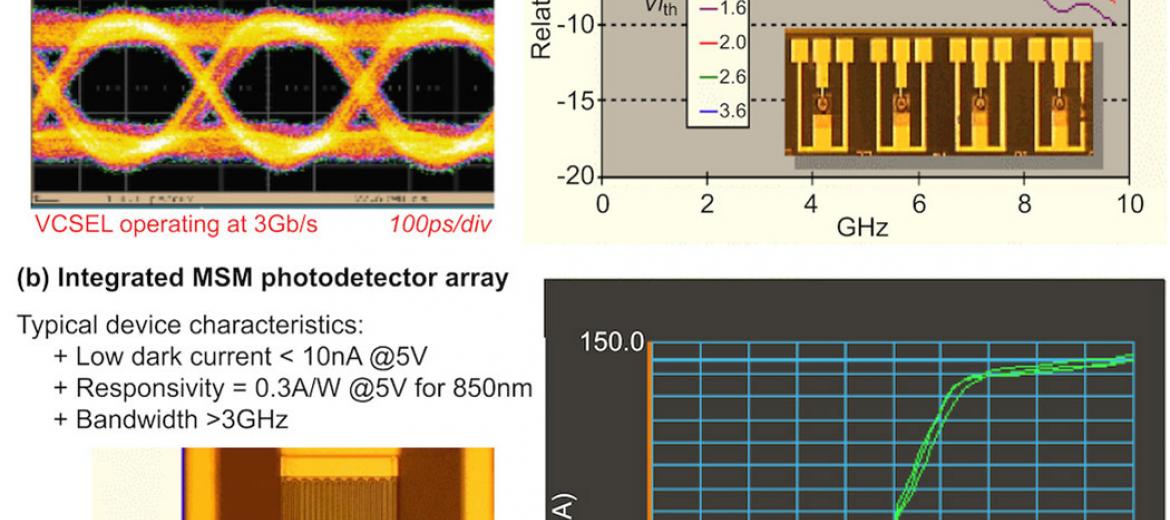

With the emergence of high-performance digital systems and the rapid growth of Internet traffic in the 1990s, the US Air Force Research Laboratory (AFRL) Micro Electronics Technology Directorate correctly predicted the growing need for optical interconnects and thus initiated several efforts to develop such technologies for the next generation of high-performance digital systems. This work was also prompted by significant advances in optical materials (i.e., III-V materials and polymers), devices (vertical-cavity surface-emitting lasers, VCSELs), and packaging technologies that were also made during this period.1 In collaboration with the Defense Advanced Research Projects Agency (DARPA) Electronic Technology Office, the AFRL thus initiated several major programs in this area.

Ireland, US team to advance integrated optoelectronics packaging

A $3 million research collaboration involving several US, Northern Ireland and Republic of Ireland institutions will seek to improve optical integrated chip technology for use in data centers. Scientists at the University of Arizona (UA) in Tucson said the goal is improving the agility of high-bandwidth optical connections that support high-capacity cloud applications.

Consortium advances solutions for high-volume chip packaging

In today’s mobile and connected world, consumers demand next-generation devices that are multi-functional, more compact, offer better performance, and consume less power. As the industry moves towards more innovative technologies to keep pace with market trends, it must also keep manufacturing costs low to remain competitive.